��늿������·���� �������Ƴ��߉���·���p�d�Ϳ��d�\�Еr�Ĺ��l�^늉������Ɲ����������߾�·�غ��l�ijɹ��ʣ��������ϵ�y��ȫ�\�У���늿������ڳ��߉����ϵ�y�еõ��V�����á�

���ښ�϶�h���F�IJ���ͣ� 늿�����늿�ֵ���Զ��^�ã� ���칤ˇ�y�Ȳ��ɱ��^�ͣ���������@���ă��c����϶�h���F��늿������F�įBƬʽ������ʽ늿������g����ָ�˺ã��r��Ҳ�ͣ� ���������ڲ�늿�����߀�����ڟoԴ����C���V�����oֹ��Դ�a�������c늿������V��늿���������늙C����늿�����늻��t�ô�늿����Ȉ��_��

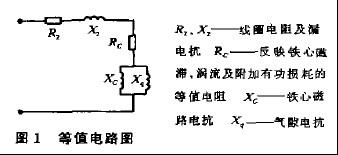

��϶�h���F��늿����ĵ�ֵ�·��ֵ�·��D1��ʾ���˵�ֵ�·���cһ���є���1�Ě�϶�h���F������������������ξ�Ȧ��������ԇ�r����r��ͬ���� ��Ǿ��ԅ����������龀�ԅ�����

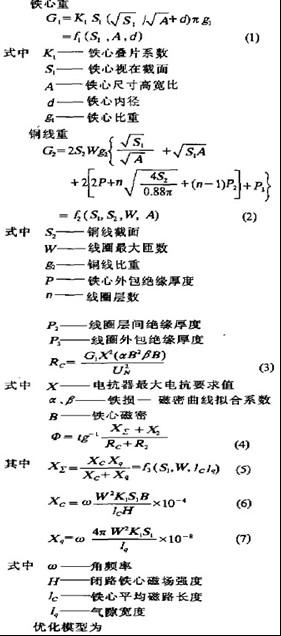

�����OӋ�����ڝM��늿����~��늉�UN��늿����迹��>89���������^늿�ֵ�����`�������S�����ļs���l���£� ����Ŀ�����~�F�ɱ����٣�

�������⣬ ���~�F�ɱ����ٕr���~�F����S��S 늿����OӋ�У���A��d�_����S��S���ȅ�������ϵ��ʽ(8)�ļs���l���Ƕ�׃���[�������y���@ʾ���������ʽ(9)��(10)������õ��������t������⡣ |